In an MPCore system, when one core is waiting for resources to be released, what instruction could be used to reduce that core's power consumption?

An ARM Cortex-A9 multi-core system has two CPUs, C1 and C2, each with a corresponding data cache. The code running on C1 writes to a memory location M. and C1 updates its data cache, but not main memory. After that, C2 tries to read the contents of memory location M. Which of the following hardware can automatically (without software inteivention) ensure that C2 reads the updated contents of M?

Which of the following ARM processors has the best energy efficiency (measured in mW/MHz)?

In which of the following scenarios would cache maintenance operations be necessary in an ARMv7 system?

A standard performance benchmark is being run on a single core ARM v7-A processor. The performance results reported are significantly lower than expected. Which of the following options is a possible explanation?

A deeply embedded real-time industrial control system is missing some hard real-time interrupt deadlines. Which of the following performance analysis techniques is the most suitable for identifying which routines are causing the problem?

What will be the contents of R2 after the execution of the following piece of code?

LDRR1, =0xAABBCCDD

MOV R2, #0x4

ANDSR1, R1, #0x4

ADDNE R2, R2, #0x4

Which one of the following features must any processor support to conform to the ARMv7-A architecture?

The Cortex-A9 processor has 6 breakpoint units and 4 watchpoint units. What is the maximum number of breakpoints the debugger can set on code in ROM?

Which of the following properties is a required characteristic of a Symmetric Multiprocessing (SMP) system?

In a single-processor system, which of these operations requires a barrier instruction to guarantee correct operation?

On a processor supporting the Security Extensions, what sequence of operations is required to move from Non-secure User mode to Secure state?

In a hardware system that runs software providing secure systems, which of the following describes the behavior of external memory and peripherals?

Which events would be counted using the Performance Monitoring Unit (PMU) in order to measure the data cache efficiency of an application?

Which one of the following statements best describes the function of vector catch logic?

When using the default ARM tool-chain libraries for bare-metal applications. I/O functionality is rerouted and handled by a connected debugger. This is often referred to as semihosting. Which one of the following explanations BEST describes how this feature can be implemented by a debugger?

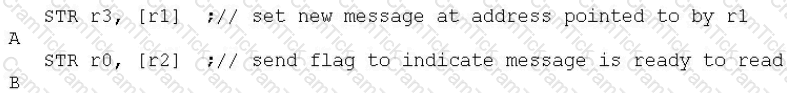

A message passing system between two CPUs is implemented using data stored in a shared area of memory. To pass a message, the first CPU executes the instructions:

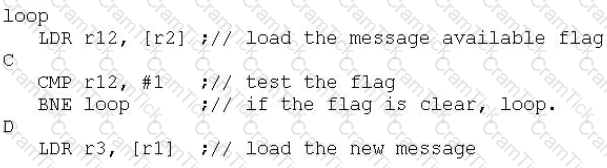

The second CPU receives the message using the instructions:

On both CPUs, r1 = 0x5000 and r2 = 0x6000. At which of the points A, B, C and D must Data Memory Barrier (DMB) instructions be placed in order to ensure messages are passed reliably and efficiently?

An ARM processor connected to a Generic Interrupt Controller (GIC) is handling an active interrupt 11. A new interrupt 12 that is received at the GIC is forwarded to the processor, and the active interrupt 11 is preempted. Which of the following possible values of 11's priority (P1), 12's priority (P2) and the processor’s priority mask (PM) permit this to happen? Assume there are 256 priority levels implemented.

The interval of time from an external interrupt request signal being raised to the first fetch of an instruction of the interrupt handler is called the interrupt:

AAE | EN0-001 Questions Answers | EN0-001 Test Prep | ARM Accredited Engineer Questions PDF | EN0-001 Online Exam | EN0-001 Practice Test | EN0-001 PDF | EN0-001 Test Questions | EN0-001 Study Material | EN0-001 Exam Preparation | EN0-001 Valid Dumps | EN0-001 Real Questions | AAE EN0-001 Exam Questions